## **Problem Statement**

Today, all the largest supercomputers are manufactured in the US and Asia, not in Europe. Mont Blanc is a newly started EU project aimed at putting Europe back on the map of supercomputer manufacturers. The goal is to build a prototype that will be ranked at the top of the Green500.org ranking list of the most energy efficient computers. Energy efficiency is already a main design constraint for supercomputers, and it is expected to become the dominating design challenge in the future. Mont Blanc will achieve energy efficiency by adopting low end processors from mobile phones and other embedded systems products. The project considers both GPUs from Nvidia, ARM-Nvidia Tegra processors and the Mali T604 (quad-core) and T658 (8-core) GPUs developed by ARM.

The main goal of the thesis is to do experiments and evaluate performance and energy-efficiency of applications using the OmpSs environment for parallel programming developed by UPC/BSC. OmpSs will be used in the Mont Blanc project and is also a central part of many other European EU-7FP research projects. Consequently, increased knowledge about OmpSs at NTNU makes it more likely that NTNU can contribute to Mont Blanc and other EU projects in the future. The following elements are included in the project:

- a) Study the OmpSs environment for parallel programming.

- b) Evaluate performance and energy-efficiency of OmpSs applications or application kernels. (The selection of applications is dependent of what OmpSs codes are made available to NTNU.)

- c) Problems should be evaluated for different problem sizes at a desktop computer equipped with an Intel core i7 (Sandy Bridge) quad-core processor. Currently, energy measurements can be done by reading the Sandy Bridge MSR energy registers.

- d) The effect of vectorization should be investigated.

- e) If time permits, and if HW is made available by ARM, energy-efficiency studies of the same OmpSs codes on ARM HW should be conducted.

- f) The report should document the work in a way that helps future students continue the with projects along the same path of research.

# Acknowledgements

First of all I would like to thank professor Lasse Natvig at NTNU for being my primary supervisor for my thesis, and giving me excellent supervision. He kept me motivated for working hard on this thesis by giving me very helpful feedback on my work, as well as providing interesting discussions and ideas at our meetings.

My thanks also goes to Jörg Wagner at the ARM office in Trondheim. He not only gave us access to ARM hardware by arranging a loan agreement between NTNU and ARM, but he also spent a significant amount of time to set up the hardware so that it was ready to use. Additionally, he gave valuable feedback on the final results.

Additionally, I would like to direct my sincere gratitudes to Jan Christian Meyer. Jan Christian spent a significant amount of time reading through my final report, and giving very high quality and useful feedback. Thanks to him, the quality of the report was significantly improved.

### Abstract

In this thesis, the performance and energy efficiency of two current hardware platforms are evaluated, the Intel Sandy Bridge Core i7 and ARM Cortex-A9 MPCore test chip, using techniques like vectorization and multi-threading with task-based programming using OmpSs. We present results from three task-based programs, Black-Scholes, FFTW and matrix multiplication on both platforms. The performance and energy efficiency is compared between different configurations of threads, vectorization and task scheduling algorithms. Energy consumption is measured using the Running Average Power Limit interface on the Sandy Bridge, and regular sampling of the current power dissipation from the system configuration registers on ARM. The energy efficiency results are presented using the metrics total energy consumed, power, GFLOPS/W, and the energy-delay and energy-delay squared products. The energy efficiency of the ARM Cortex-A9 MPCore is compared to that of Sandy Bridge using the process-normalized energy-delay and energy-delay squared products, as well as GFLOPS/W and energy.

Black-Scholes is adapted to use vector code, and FFTW is compiled with and without vector support. The matrix multiplication application uses ATLAS, which already is vectorized. Code for sampling and numerically integrating the power dissipation over time was developed for ARM, then different task scheduling algorithms are explored for each application.

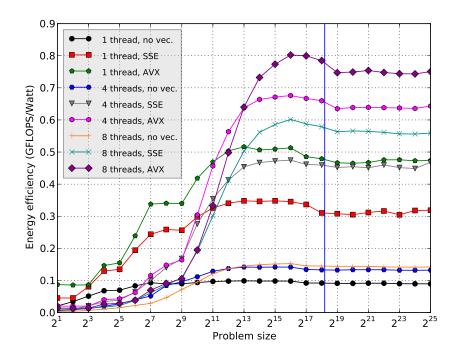

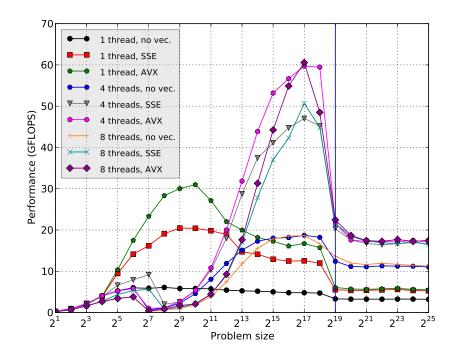

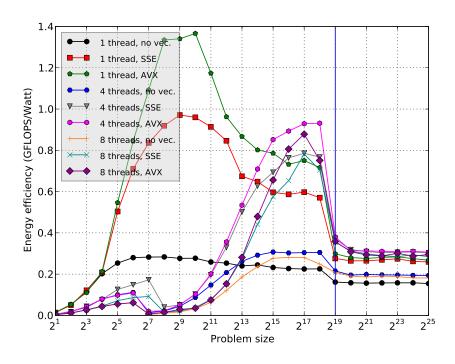

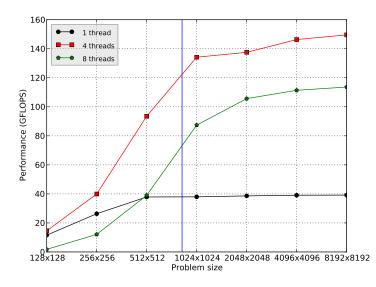

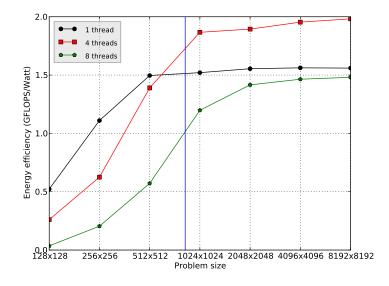

For both platforms, vectorization with SSE/AVX and NEON is found to consume little to no extra energy per second while giving significantly higher performance. Multi-threading gives higher performance, but with higher power consumption. With AVX on Intel, Black-Scholes shows an energy efficiency of 0.82 GFLOPS/W, FFTW up to 1.4 GFLOPS/W, and matrix multiplication almost 2 GFLOPS/W. Both multi-threading and vectorization significantly reduced the energy-delay products, showing up to 99.55% reduction for Black-Scholes and 93.65% for FFTW compared to non-vectorized single-threaded code for the Intel platform. The ARM results are restricted from publishing, but can be found in appendix A for those with access.

Single-threaded execution is shown to give a better GFLOPS/W for small problem sizes in the benchmarked applications, while the EDP is reduced for multi-threading even for small problems. Black-Scholes show increased performance and energy efficiency with hyper-threading. FFTW shows no significant difference using hyper-threads compared to four threads. The performance and energy efficiency for matrix multiplication is lower when hyper-threading is used.

## Abstract (Norwegian)

I denne oppgaven evalueres ytelse og energieffektivitet for to moderne maskinvareplatformer, Intel Sandy Bridge Core i7 og ARM Cortex-A9 MPCore test chip. Teknikker som vektorisering og multitråding brukes sammen med task-basert programmering i OmpSs. Vi presenterer resultater fra tre task-baserte programmer, Black-Scholes, FFTW og matrisemultiplikasjon på begge plattformer hvor ytelse og energieffektivitet sammenlignes for forskjellige konfigurasjoner av tråder, vektorisering og task-schedulingalgoritmer. Energibruk blir målt ved bruk av Running Average Power Limit-grensesnittet på Sandy Bridge, og ved jevnlig sampling av effekt ved bruk av systemkonfigurasjonsregistere på ARM. Resultater for energieffektivitet presenteres ved bruk av metrikker som total energibruk, effekt, GFLOPS/W, og energy-delay- og energy-delay-squared produkter. Energieffektiviteten på ARM Cortex-A9 MPCore sammenlignes med Sandy Bridge ved bruk av prosess-normalisert energy-delay og energy-delay squared, samt GFLOPS/W og energi.

Black-Scholes blir tilpasset til å bruke vektorkode, og FFTW ble kompilert med og uten vektorstøtte. Matrisemultiplikasjonsapplikasjonen bruker ATLAS som allerede er vektorisert. En algoritme for sampling og integrering av effekt ble utviklet for ARM. Forskjellige task-scheduling-algoritmer ble utforsket for å finne en optimal algoritme for hver applikasjon.

For begge plattformer viser vektorisering med SSE/AVX og NEON seg å bruke fra liten til ingen ekstra energi per tidsenhet sammenlignet med ikke-vektorisert kode. Multitråding gir høyere ytelse, men også et betydelig høyere effektforbruk. Med AVX på Intel-plattformen viser Black-Scholes en energieffektivitet på 0.82 GFLOPS/W, FFTW up til 1.4 GFLOPS/W, og matrisemultiplikasjon nesten 2 GFLOPS/W. Både multithreading og vektorisering reduserte energy-delay-produktet betydelig, med opp til 99.55% reduksjon for Black-Scholes og 93.65% for FFTW sammenlignet med ikke-vektorisert entrådet kode på Intel-plattformen. ARM-resultatene er unntatt publisering, men finnes i appendix A for de med tilgang.

Kjøring på èn tråd viser seg å gi høyere GFLOPS/W for små problemstørrelser i applikasjonene som er testet, mens EDP er redusert med flertråding selv for små problemer. Black-Scholes viser økt ytelse og energieffektivitet med hyper-tråding. FFTW viser ingen vesentlig forskjell ved å bruke hypertråder. Både ytelse og energieffektivitet for matrisemultiplikasjon er lavere når hyper-tråding er brukt.

# Contents

| A  | cknov   | wledgements iii                                       | i |

|----|---------|-------------------------------------------------------|---|

| A  | bstrac  | ct v                                                  | 7 |

| A  | bstrac  | et vi                                                 | i |

| С  | onten   | ts ix                                                 | ( |

| Li | st of ] | Figures xiii                                          | i |

| Li | st of ' | Tables xv                                             | 7 |

| 1  | Intr    | oduction 1                                            | L |

|    | 1.1     | Motivation                                            | L |

|    | 1.2     | Thesis Scope and Goals                                | , |

|    | 1.3     | Terminology                                           |   |

|    | 110     | 1.3.1   Performance Measurements and FLOPS   2        |   |

|    | 1.4     | Contributions                                         |   |

|    | 1.5     | Thesis Outline   3                                    |   |

| 2  | Bacl    | kground                                               | 5 |

|    | 2.1     | The Mont Blanc Project and Exascale Computing         | 5 |

|    |         | 2.1.1 Challenges for exascale supercomputers          | 5 |

|    |         | 2.1.2 The Mont Blanc project                          | 5 |

|    | 2.2     | OpenMP Super Scalar (OmpSs)                           | 7 |

|    |         | 2.2.1 Task-based programming                          | 3 |

|    |         | 2.2.2 Heterogeneous capabilities                      | ) |

|    |         | 2.2.3 Nanos++ and Mercurium                           | ) |

|    |         | 2.2.4 OmpSs in Mont Blanc                             | ) |

|    |         | 2.2.5 Task scheduling and scheduling algorithms       | ) |

|    | 2.3     | Single Instruction, Multiple Data (SIMD)              |   |

|    |         | 2.3.1 Streaming SIMD extensions (SSE)                 |   |

|    |         | 2.3.2       Advanced Vector Extensions (AVX)       13 |   |

|    |         | 2.3.3 ARM Advanced SIMD Extensions (NEON)             |   |

|    | 2.4     | Energy Efficiency Metrics                             |   |

|    |         | 2.4.1   Energy and power   15                         |   |

|    |         |                                                       |   |

|   |     | 2.4.2   | GFLOPS/W                                                          | 15 |

|---|-----|---------|-------------------------------------------------------------------|----|

|   |     | 2.4.3   | Energy-delay products                                             | 15 |

|   | 2.5 | Relate  | ed Work                                                           | 16 |

|   |     | 2.5.1   | The Energy Efficiency of CMP vs SMT for Multimedia Workloads .    | 16 |

|   |     | 2.5.2   | Energy per Instruction Trends in Intel®Microprocessors            | 17 |

|   |     | 2.5.3   | Evaluation of OpenMP Task Scheduling Strategies                   | 17 |

|   |     | 2.5.4   | Parallelization of Black-Scholes and dense matrix-matrix multiply |    |

|   |     |         | using OmpSs                                                       | 17 |

|   |     | 2.5.5   | Benchmarking of FFTW                                              | 18 |

|   |     | 2.5.6   | Energy efficiency of IRAM architectures                           | 18 |

|   |     | 2.5.7   | Green500                                                          | 18 |

|   |     | 2.5.8   | Energy-saving mobile processor architectures                      | 18 |

| 3 |     |         | n Kernels                                                         | 19 |

|   | 3.1 |         |                                                                   |    |

|   | 3.2 |         | t Fourier Transform in the West (FFTW)                            |    |

|   | 3.3 | Dense   | General Matrix-Matrix Multiplication and ATLAS                    | 22 |

| 4 | -   | lement  |                                                                   | 25 |

|   | 4.1 | Energy  | 5                                                                 |    |

|   |     | 4.1.1   | Sandy Bridge                                                      |    |

|   |     | 4.1.2   |                                                                   | 26 |

|   | 4.2 |         | g of SSE log and exp to AVX and NEON                              |    |

|   |     | 4.2.1   | Porting to AVX                                                    |    |

|   |     | 4.2.2   | Porting to NEON                                                   |    |

|   | 4.3 |         | Scholes                                                           | 31 |

|   |     | 4.3.1   | Vectorization                                                     |    |

|   | 4.4 |         | t Fourier Transform in the West                                   |    |

|   |     | 4.4.1   | Modifications to the FFTW library                                 |    |

|   |     | 4.4.2   | Implementation of the benchmark                                   |    |

|   | 4.5 | Matrix  | x Multiplication                                                  | 35 |

| 5 | Exp | eriment | t Setup and Methodology                                           | 37 |

|   | 5.1 | Test Be | ench                                                              | 37 |

|   |     | 5.1.1   | Hardware                                                          | 37 |

|   |     | 5.1.2   | Software and Libraries                                            | 39 |

|   |     | 5.1.3   | Compiler and compiler flags                                       | 40 |

|   | 5.2 | Experi  | iment Methodology                                                 | 41 |

|   |     | 5.2.1   | Energy Measurements                                               | 41 |

|   |     | 5.2.2   | Experiments                                                       | 41 |

|   |     | 5.2.3   | Cache behavior experiments                                        | 44 |

|   | 5.3 |         | ing FLOPS Counts                                                  | 45 |

|   | 5.4 | Proble  | em Sizes and Memory Footprints                                    | 46 |

|   | 5.5 | Statist | ical Metrics                                                      | 46 |

|   |     |         |                                                                   |    |

<u>x</u>

|    | 6.1   | Black-Scholes: Scheduling and Variability in Nanos++ Version 0.6a | 50               |

|----|-------|-------------------------------------------------------------------|------------------|

|    | 6.2   | Black-Scholes Results                                             | 54               |

|    |       | 6.2.1 Performance                                                 | 55               |

|    |       | 6.2.2 Energy efficiency                                           | 57               |

|    |       | 6.2.3 Discussion                                                  | 61               |

|    | 6.3   | FFTW                                                              | 51               |

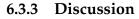

|    |       | 6.3.1 Performance                                                 | 61               |

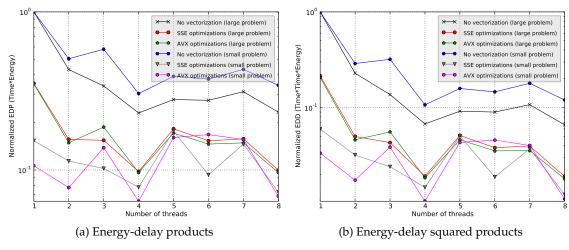

|    |       | 6.3.2 Energy efficiency                                           | 64               |

|    |       | 6.3.3 Discussion                                                  | 68               |

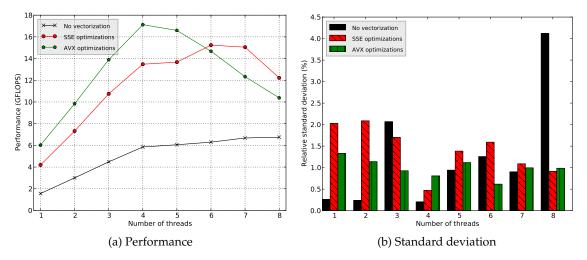

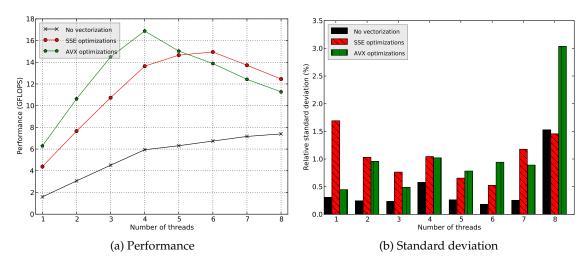

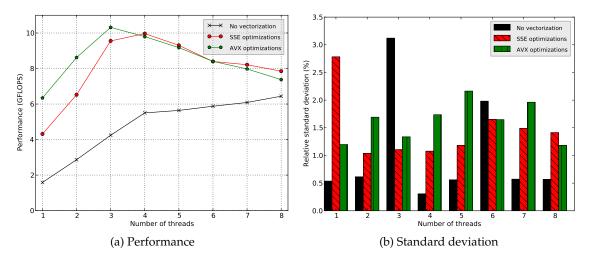

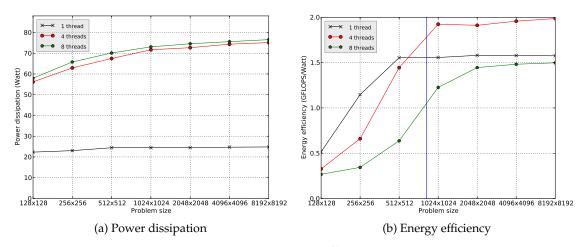

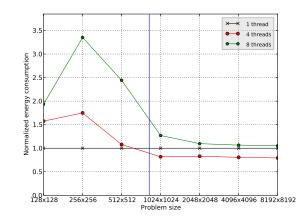

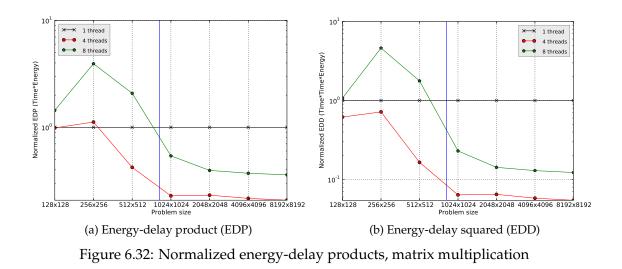

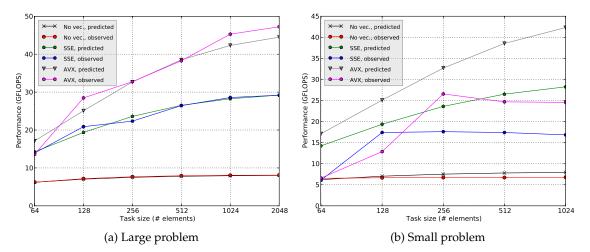

|    | 6.4   | Matrix multiplication                                             | 59               |

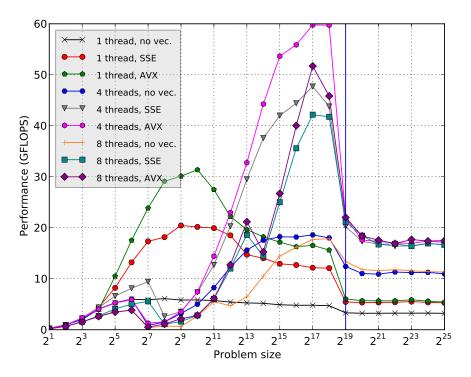

|    |       | 6.4.1 Performance                                                 |                  |

|    |       |                                                                   | 70               |

| 7  | Perf  | ormance Modelling and Discussion                                  | 73               |

|    | 7.1   |                                                                   | 73               |

|    |       | 7.1.1 Task creation and scheduling                                | 73               |

|    |       | Ŭ                                                                 | 75               |

|    | 7.2   |                                                                   | . c<br>77        |

|    | /     |                                                                   | . <i>.</i><br>77 |

|    |       | 1                                                                 | <br>77           |

|    |       |                                                                   | 78               |

| 8  | Con   | clusion                                                           | 81               |

| 0  | 8.1   | Scheduling                                                        |                  |

|    | 8.2   | Vectorization                                                     |                  |

|    | 8.3   | Multi-threading                                                   |                  |

|    | 8.4   |                                                                   | 82               |

|    | 8.5   | Conclusion - ARM                                                  |                  |

|    | 8.6   | Future Work                                                       |                  |

|    | 0.0   |                                                                   |                  |

|    |       | <ul><li>8.6.1 Full system energy measurement</li></ul>            |                  |

|    |       |                                                                   |                  |

|    |       |                                                                   | 83               |

|    |       | 11                                                                | 83<br>04         |

|    | 8.7   | 8.6.5 Energy-efficient algorithms                                 | 84<br>84         |

| ۸. | openc |                                                                   | 85               |

| A  | ppend |                                                                   | 55               |

| A  | Perf  | ormance and Energy Efficiency Results - ARM                       | 87               |

| B  | Tabı  | lated Data                                                        | 89               |

| С  | AVX   | Enabled Logarithms and Exponential Functions 10                   | 01               |

| D  | NEC   | N Enabled Logarithms and Exponential Functions 10                 | 05               |

| E  |       |                                                                   | 09               |

|    | 202   |                                                                   |                  |

| F  | FFT   | W Impl  | lementation with OmpSs                         | 117 |

|----|-------|---------|------------------------------------------------|-----|

| G  | Expe  | eriment | t Framework                                    | 119 |

|    | G.1   | Experi  | ment Scripts                                   | 119 |

|    |       | G.1.1   | Experiment specification files and test suites | 119 |

|    |       | G.1.2   | Database layout                                | 121 |

|    |       | G.1.3   | Adding support for more benchmarks             | 122 |

|    | G.2   | Result  | s Extraction and Presentation                  | 122 |

| н  | Pape  | er      |                                                | 125 |

| Re | feren | ices    |                                                | 137 |

# **List of Figures**

| 3.1<br>3.2 | Sine wave with high frequency noise                                          | 21<br>21 |

|------------|------------------------------------------------------------------------------|----------|

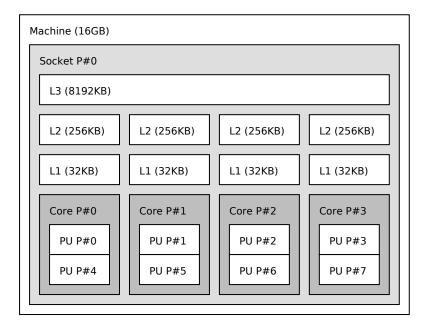

| 5.1        | Diagram of caches, cores and hyper-threads on sif                            | 38       |

| 5.2        | Diagram of caches, cores and memory on the ARM board                         | 39       |

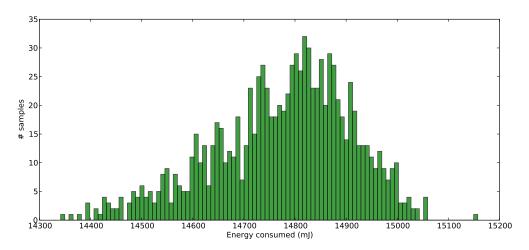

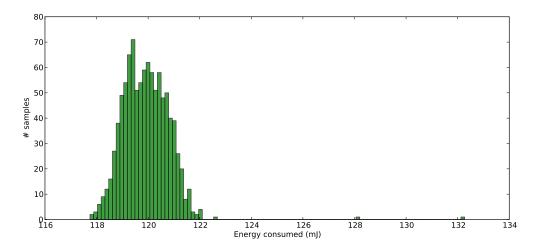

| 5.3        | Distribution of sample values from MSR consistency test                      | 43       |

| 5.4        | Distribution of sample values from energy measurements using sampling on     |          |

|            | ARM                                                                          | 44       |

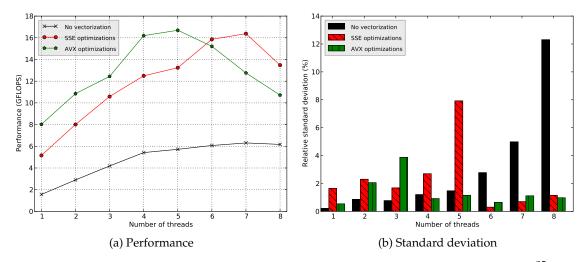

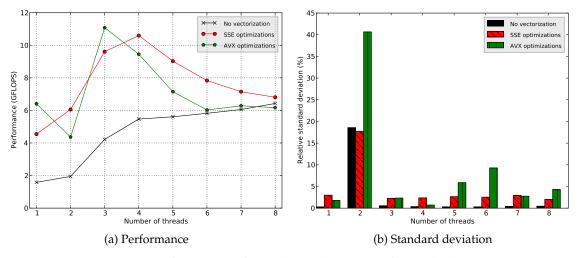

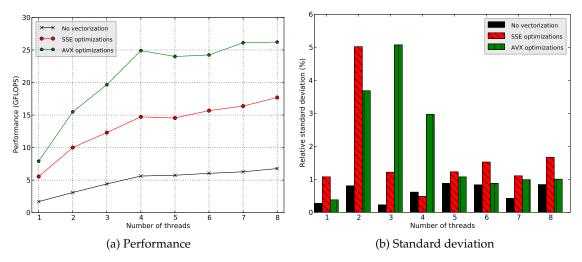

| 6.1        | Performance with regards to number of threads, Black-Scholes, N= $2^{25}$    | 51       |

| 6.2        | Performance with regards to number of threads, Black-Scholes, $N=2^{13}$     | 51       |

| 6.3        | Performance of small problem, distributed breadth-first scheduling           | 52       |

| 6.4        | Performance of small problem, work-first scheduling                          | 52       |

| 6.5        | Performance of small problem, default scheduling, no spinning                | 53       |

| 6.6        | Performance of small problem, distributed breadth-first scheduling, no spin- |          |

|            | ning                                                                         | 53       |

| 6.7        | Performance of small problem, work-first scheduling, no spinning             | 54       |

| 6.8        | Performance with different task sizes, no spinning                           | 54       |

| 6.9        | Performance of large problem with different task sizes, 8 threads            | 55       |

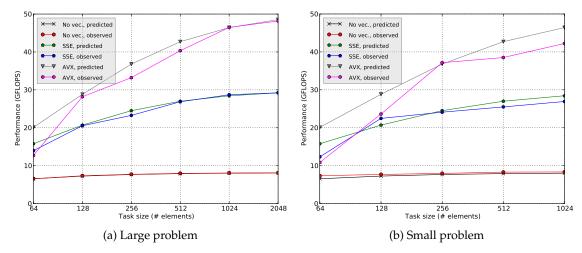

| 6.10       | Performance of small problem with different task sizes, 8 threads            | 55       |

|            | Performance of large problem with task size 2048, DBF scheduling             | 56       |

| 6.12       | Performance of small problem with task size 256, DBF scheduling              | 56       |

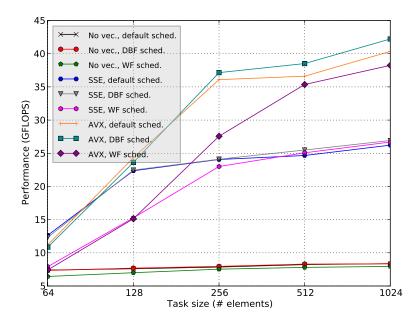

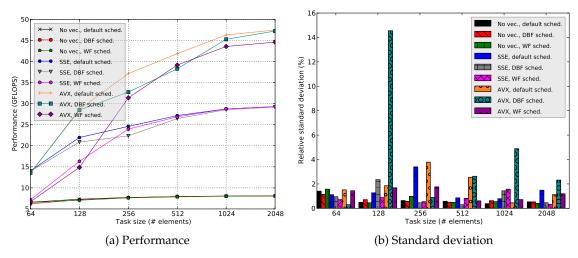

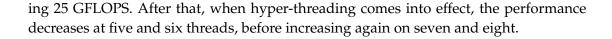

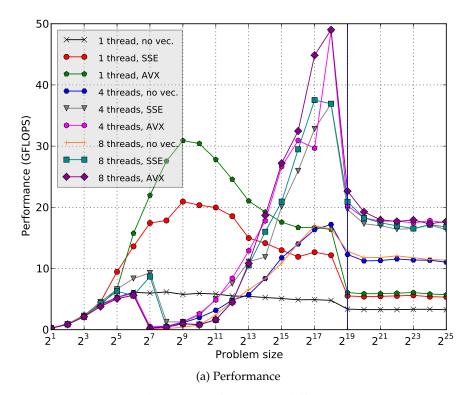

| 6.13       | Performance of Black-Scholes at different problem sizes                      | 57       |

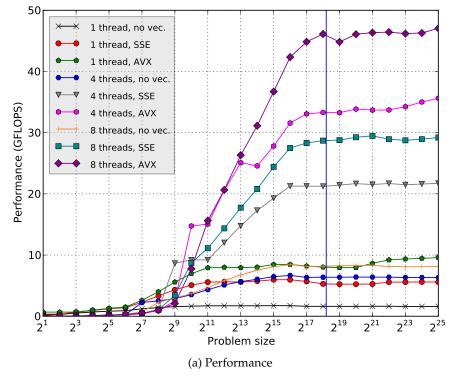

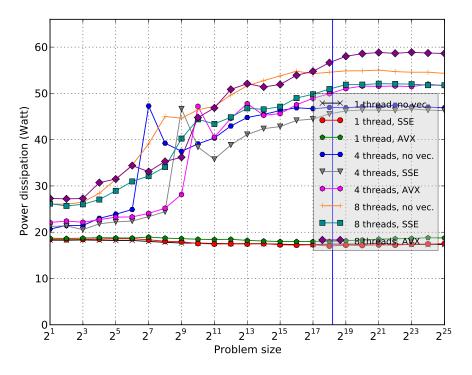

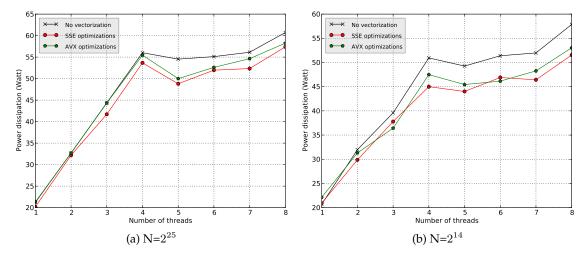

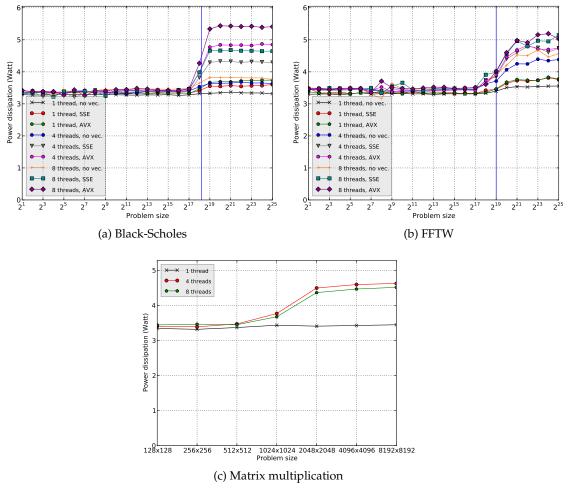

| 6.14       | Power dissipation with varying number of threads, Black-Scholes              | 58       |

|            | Power dissipation, Black-Scholes                                             | 58       |

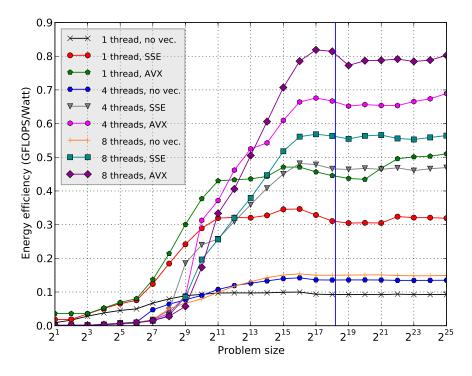

|            | GFLOPS/W, Black-Scholes                                                      | 59       |

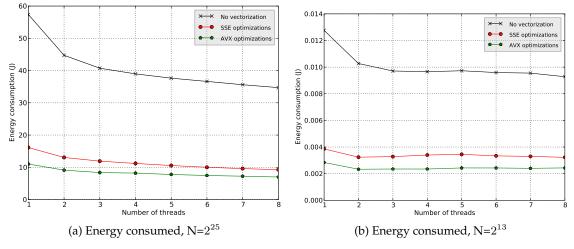

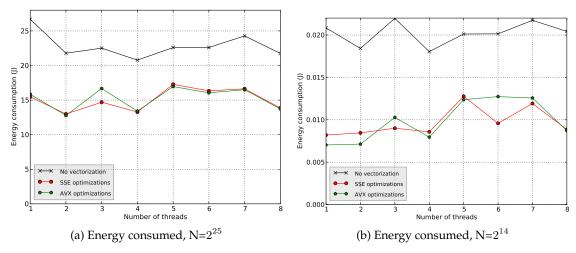

|            | Energy consumed for the whole problem, Black-Scholes                         | 60       |

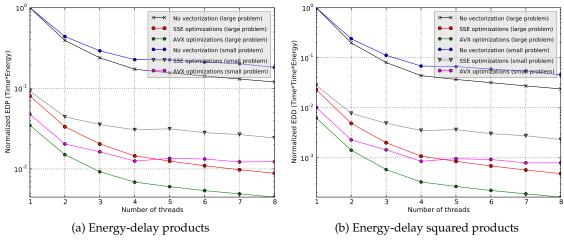

| 6.18       | Normalized energy-delay products, Black-Scholes                              | 60       |

|            | Performance with different scheduling algorithms, FFTW                       | 62       |

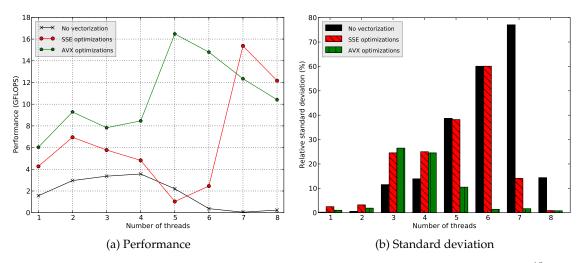

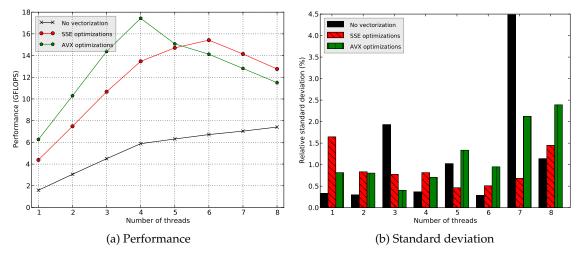

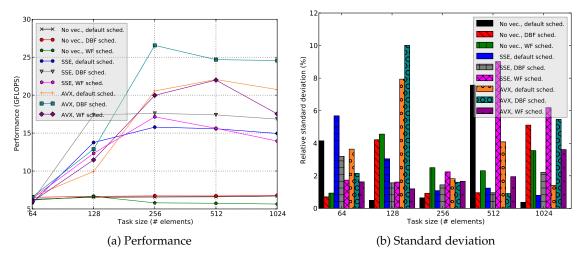

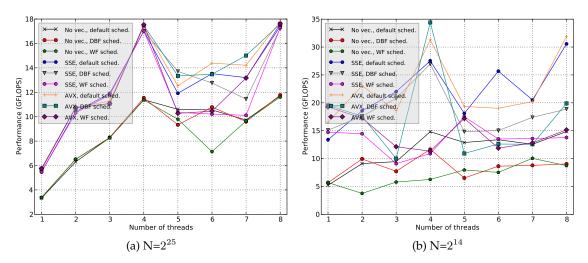

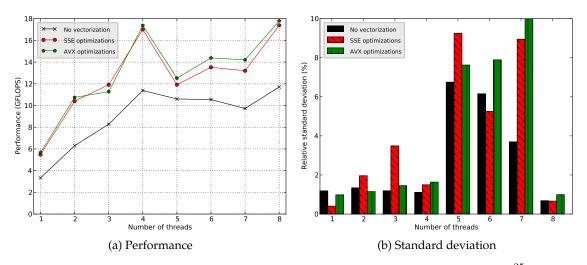

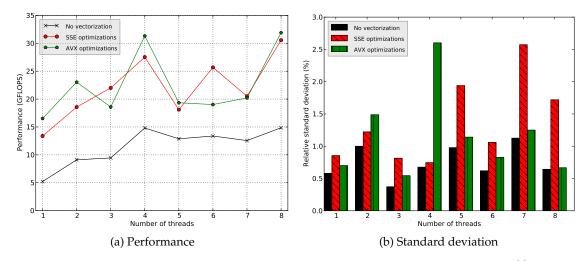

|            | Performance with regards to number of threads, FFTW, N= $2^{25}$             | 62       |

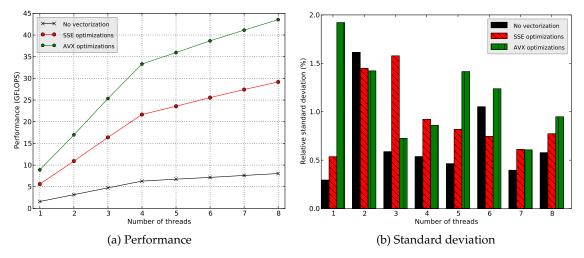

|            | Performance with regards to number of threads, FFTW, N= $2^{14}$             | 63       |

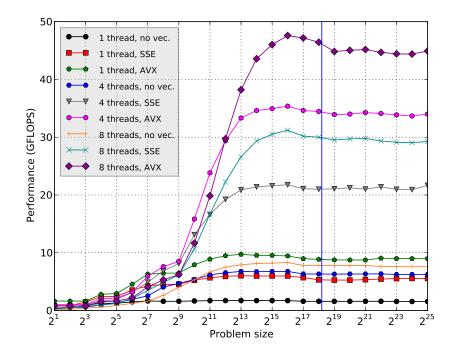

|            | Performance of FFTW at different problem sizes                               |          |

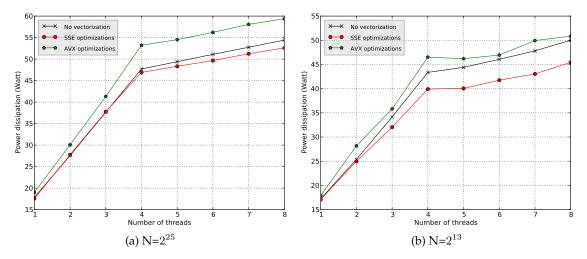

|            | Power dissipation with varying number of threads, FFTW                       | 64       |

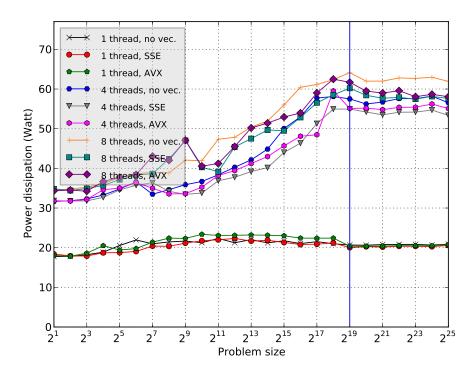

|            | Power dissipation, FFTW                                                      | 65       |

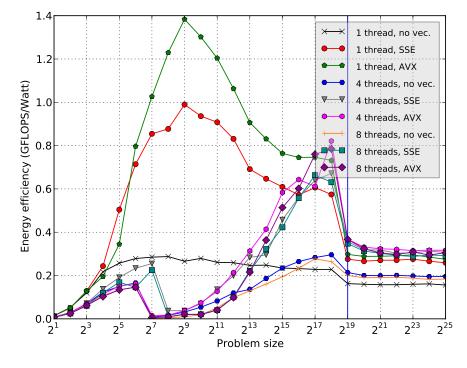

| 6.25       | GFLOPS/W, FFTW                                                               | 66       |

# **List of Tables**

| 2.1                                                                 | List of exascale applications targeted for porting to Mont Blanc (taken from [1])      | 7                                                                                                                                                          |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2                                                                 | List of scientific libraries targeted for porting to Mont Blanc                        | 7                                                                                                                                                          |

| 4.1<br>4.2                                                          | Overview of the SYS_CFGCTRL register                                                   | 26<br>35                                                                                                                                                   |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10 | Hardware specifications for sif                                                        | <ul> <li>38</li> <li>38</li> <li>39</li> <li>39</li> <li>40</li> <li>40</li> <li>43</li> <li>43</li> <li>44</li> <li>46</li> </ul>                         |

| 6.1                                                                 | Result presentation order                                                              | 50                                                                                                                                                         |

| B.1                                                                 | Black-Scholes, performance with eight threads, DBF scheduling, different               |                                                                                                                                                            |

| B.11                                                                | black-Scholes, performance with eight threads, DDF scheduling, different<br>task sizes | <ul> <li>89</li> <li>90</li> <li>91</li> <li>92</li> <li>93</li> <li>94</li> <li>95</li> <li>96</li> <li>97</li> <li>98</li> <li>99</li> <li>99</li> </ul> |

| G.1 | Reserved keywords/variables in the experiment framework | 120 |

|-----|---------------------------------------------------------|-----|

| G.2 | Required member functions of test suites                | 123 |

# Chapter 1

### Introduction

In this chapter, the motivation and goals for the thesis is presented, then the contributions from this work are outlined. Additionally, some terminology will be explained, and an outline of the chapters is presented.

#### 1.1 Motivation

Energy requirements is one of the major challenges for large supercomputers [2]. If the most powerful supercomputer as per November 2011 were scaled to one exaFLOPS without improving energy efficiency, it would require more than a gigawatt of power, enough to power almost a million homes. Not only is this impractical due to the cost of operation, but each component must also be cooled which also incurs a significant cost in equipment and additional energy use, further increasing operational costs.

The Mont Blanc project is an EU project aimed at reaching the exaFLOPS milestone by using energy efficient embedded accelerators, for instance the ARM Mali GPUs, in order to get the energy efficiency of the computer up to a level where this is possible. The first goal is 7 GFLOPS/W and a total performance of 50 petaFLOPS by 2014. For 2017, the goal is 20 GFLOPS/W by 2017, approaching the goal of 50 GFLOPS/W required for an exaFLOPS computer with a power budget of 20MW.

Although much of the improvement must come from advances in hardware, the software also matters. Often, energy efficiency and performance are closely related, in that higher performance often gives higher energy efficiency, given that the hardware configuration stays the same. However, this may not always be true; in this project it was found that vectorizing codes consumes little to no extra energy for a significant performance boost, while multi-threading involves activating more cores, incurring significantly higher energy usage.

This thesis is the result of the first in a series of research projects exploring energy efficiency in modern computer architectures. First we present the results from strictly on-chip energy usage, where most of the execution occurs on-chip with minimal interaction from the memory system. Future research projects will measure the energy consumption of the full computing system, before expanding to energy measurements on multi-node computing clusters. The ultimate goal is to try to understand the energy implications of every subsystem, and use that knowledge to develop methods for more energy efficient computers, both through improvements in software and in hardware.

#### **1.2** Thesis Scope and Goals

The goal of this thesis is to evaluate current hardware platforms with respect to energy efficiency and performance using techniques like vectorization and multi-threading with task based programming using OmpSs. The CPUs used in the experiments are the Intel Sandy Bridge CPU Core i7 2600 and a development implementation of the ARM Cortex-A9 MPCore quad-core CPU. The Sandy Bridge architecture is the latest generation of Intel CPUs before Ivy Bridge, which was released in April 2012, and the Cortex-A9 is relevant in many embedded devices like cell phones. Before evaluating energy efficiency, the applications are first optimized for performance.

It is also of interest to compare the ARM and Intel platforms, in particular because the Sandy Bridge is a relatively new architecture that is claimed to reach "new levels of performance, flexibility and energy efficiency" by Intel [3], and ARM is relevant in many mobile and embedded devices where energy efficiency is a key point.

### 1.3 Terminology

#### 1.3.1 Performance Measurements and FLOPS

In this work, FLOPS with capital letters is used to refer to the rate of computation, i.e. FLoating-point OPerations per Second. When talking about the quantity "number of floating point operations", either "floating point operation(s)", or "flop(s)" in lower case, is be used.

#### 1.4 Contributions

The contributions of this work are:

- 1. Performance and energy efficiency results for three applications, Black-Scholes, FFTW and matrix multiplication for both ARM Cortex-A9 MPCore test chip and Intel Core i7 2600.

- Comparisons of the energy efficiency for these two CPUs using the metrics energy, GFLOPS/W, process-normalized energy-delay and energy-delay squared product.

- Models for performance in task-based programs based on task scheduling overhead and memory overhead.

- 4. A research paper presenting the Sandy Bridge results with the GFLOPS/W metric. The paper is going to be published in the LNCS 7453 proceedings, and presented at the EECS section of the ICT-GLOW 2012 conference. It is attached in appendix H.

- 5. A benchmarking framework that was developed because of the large number of benchmarks that was run and had to be managed throughout the writing of this thesis. This framework is briefly described in appendix G.

The division of work for the research paper is as follows: Hallgeir Lien provided the results, the research infrastructure and wrote several parts of the paper, especially the discussion. Lasse Natvig provided the main paper structure, and wrote other parts of the paper, using the then current version of Hallgeir Lien's thesis as main source. Abdullah Al Hasib started the work on energy measurements using MSRs and did some contributions to the text, while Jan Christian Meyer acted both as scientific discussion partner in the final stages of the work, and also helped improving the text before submission and for the camera ready copy. The work will be presented at ICT-GLOW in September 2012.

#### **1.5** Thesis Outline

This thesis is structured as follows. Chapter 2 gives a background in the central topics of this paper: Mont Blanc, OmpSs, challenges in large supercomputers, heterogeneous computing, vectorization (SSE, AVX and NEON), energy metrics, and related work. Chapter 3 give an overview of the benchmarked applications, Black-Scholes, FFTW and matrix multiplication. Chapter 4 explains the implementation details for each application or benchmark. Chapter 5 covers methodology and experiment setup: Compiler flags used, software versions, hardware, statistical metrics and how energy measurements were performed. Chapter 6 presents the performance and energy efficiency results for all three applications, with some discussion of each result. Chapter 7 presents a derivation of a model for performance where task creation and scheduling overheads are taken into account, and a model estimating overhead of main memory accesses for each application. Chapter 8 concludes with a summary of the main results, and a conclusion. Appendix A presents the performance results for the ARM processor. The appendix is restricted from publishing, so it is provided as an attachment to this report.

# Chapter 2

## Background

In this chapter background on the tools and programming models used will be given. The Mont Blanc project is also presented. The chapter is organized as follows: Section 2.1 gives an overview of exascale computing, the Mont Blanc project and its goals. Section 2.2 gives an introduction to the OmpSs programming model developed at the Barcelona Supercomputing Center and the relevance it has for this thesis. Section 2.3 explains the concepts behind SIMD and how this is implemented in the Intel Sandy Bridge CPUs. Section 2.4 presents different metrics that are used for evaluating energy efficiency. Lastly, section 2.5 gives an overview of related work and their results.

### 2.1 The Mont Blanc Project and Exascale Computing

A major milestone for supercomputers is hitting the exaFLOPS mark in performance. Today's most powerful supercomputer is rated to just over 10 petaFLOPS [4]. A hundredfold improvement in performance is required to reach one exaFLOPS. This presents a number of challenges. The Mont Blanc project, a part of the European Exascale Software Initiative [5], is one of the projects trying to address some of the challenges in exascale computing.

#### 2.1.1 Challenges for exascale supercomputers

Developing an exascale supercomputer requires significant technological advances in many areas [2]. For instance, the performance gap between memory, storage systems and CPUs is growing [6]. If memory systems and interconnects are unable to scale with the CPU development, bandwidth will be a serious bottleneck in an exascale computer.

Another challenge the supercomputing community is facing is the increased complexity of writing software for large computing clusters in the presence of the CPUmemory performance gap and heterogeneous systems. In order to minimize the performance impact of data movement, it has proved useful to overlap computation with communication time in clusters [7][8][9]. Some research has been conducted in automatically taking care of this overlap through alternative programming models. Tarragon [10] developed at UC San Diego is one such approach that is an actor based execution model where the programmer defines a partial ordering of tasks, and the runtime system will then take care of scheduling these tasks on physical processors.

One of the most significant barriers that supercomputers face today is power dissipation [2]. The most powerful supercomputer as of November 2011 as listed by the Top 500 website [4], K Computer at the RIKEN Advanced Institute for Computational Sciences (AICS) in Japan, has a theoretical peak performance of 11.3 petaFLOPS and draws 12.66 megawatts of power, giving a energy efficiency of 0.89 GFLOPS/W. If we were to scale this linearly up to one exaFLOPS, we get a power requirement of 1.12 GW. On the other hand, using the most energy efficient supercomputer, the IBM BlueGene/Q, Power BQC at the IBM Rochester site [11] uses 2.02 GFLOPS/W, giving a power requirement of 495MW for one exaFLOPS. A more reasonable power budget is 20 MW [12], which would require an efficiency of 50 GFLOPS/W, a 25x increase in energy efficiency from the energy efficiency leader as per the Green500 list, November 2011 [11].

#### 2.1.2 The Mont Blanc project

The Mont Blanc project, one of three projects under the European Exascale Software Initiative (EESI), is a project with the ultimate goal of building an exascale supercomputer. Mont Blanc has three main objectives: [1]

- 1. Deploying a prototype HPC system based on existing energy efficient embedded technologies, scalable to 50 petaFLOPS using only 7 MW of power, competitive on the Green 500 list in 2014.

- Designing a next-generation HPC system based on new embedded technologies, overcoming some or most of the limitations of the previous generation. This system will be scalable to 200 petaFLOPS at 10 MW, competitive for the Top 500 list by 2017.

- 3. Porting and optimizing a small number of representative exascale applications for use on this new system, as well as some important scientific libraries. A preliminary list of these applications can be found in table 2.1, and the libraries have been listed in table 2.2.

As mentioned in the previous section, the most energy efficient supercomputer per November 2011 according to the Green 500 list has an efficiency of 2.02 GFLOPS/W [11]. However, the first objective of Mont Blanc is to achieve more than 7 GFLOPS/W, more than tripling this efficiency. The next objective by 2017 is improving this to 20 GFLOPS/W, approaching the 50 GFLOPS/W goal required for an exascale supercomputer with a power budget at 20 MW. In order to achieve this kind of energy efficiency, heterogeneous computing, i.e. offloading parts of the work to accelerators like graphics processing units (GPUs), plays an important role. It is already known that in terms of performance per watt, GPUs are highly efficient when fast on-chip memory is used, on applications with high parallelism where a single operation is performed on many data elements at a time [13]. Mont Blanc aims to use energy efficient accelerators like the

| Application     | Description                    |

|-----------------|--------------------------------|

| YALES2          | Fluid dynamics                 |

| EUTERPE         | Fluid dynamics                 |

| SPECFEM3D       | Seismic wave propagation       |

| MP2C            | Multi-particle collisions      |

| BigDFT          | Electronic structure           |

| QuantumESPRESSO | Electronic structure           |

| PEPC            | Coulomb + gravitational forces |

| SMMP            | Protein folding                |

| ProFASI         | Protein folding                |

| COSMO           | Meteorological modeling        |

| BQCD            | Quantum ChromoDynamics         |

Table 2.1: List of exascale applications targeted for porting to Mont Blanc (taken from [1])

| Library                                                                           | Description                                                                                                                                        |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| ATLAS                                                                             | Automatically Tuned Linear Algebra Software. Provides high perfor-<br>mance BLAS (Basic Linear Algebra Subprograms) APIs for C and Fortran<br>[16] |

| FFTW Fastest Fourier Transform in The West. For computing Fast Fourier forms [17] |                                                                                                                                                    |

| HDF5                                                                              | Hierarchical Data Format version 5. A file format and interfaces for storing large amounts of numerical data [18]                                  |

| LAPACK                                                                            | Linear Algebra PACKage. A library providing numerical linear algebra routines, e.g. equation solvers and matrix decompositions [19]                |

| MAGMA                                                                             | Magma Computational Algebra System. Computer algebra system for solving problems in algebra, number theory, geometry and combinatorics [20]        |

Table 2.2: List of scientific libraries targeted for porting to Mont Blanc

ARM Mali series of GPUs, which is often used in embedded devices like cell phones [14]. These devices are not designed for HPC and have never been used for such, which is one challenge that the Mont Blanc project aims to address [15].

### 2.2 **OpenMP Super Scalar (OmpSs)**

OpenMP (Open Multi-Processing) is a widely used application programming interface for multi-threaded applications in shared memory computers. Compared to many other APIs like pthreads or MPI, OpenMP requires little extra code for adding multiprocessing to the program, which increases the programmer's productivity compared to those other APIs [21]. However, OpenMP is usually implemented for shared-memory multiprocessors, and those implementations cannot be used across nodes in a supercomputer without a virtualization layer like e.g. vSMP [22], or for accelerators like GPUs. For computing clusters, MPI has been the *de facto* standard programming model, and for GPUs or accelerators, both CUDA, for NVIDIA GPUs, and OpenCL are widely used. However, these programming models involve additional work for the programmer with memory allocation, data movement, device queries, error handling, and so on. As supercomputers grow, this process gets more difficult, which distracts the programmer from the productive work of actually implementing the kernels. There has been some research on programming models to handle heterogeneous architectures, like the Mint programming model and OpenMPC [23][24]. However, those approaches are specialized on only one architecture (NVIDIA GPUs), and they are only efficient on certain types of kernels.

OpenMP Super Scalar (OmpSs for short) is a task-based programming model developed at the Barcelona Supercomputing Center (BSC). The goal of OmpSs is to address the issue of complexity in the development of applications for computing clusters and heterogeneous architectures by providing extensions to OpenMP [25].

#### 2.2.1 Task-based programming

This section will attempt to explain the purpose of and need for task-based programming.

In OpenMP, the programmer would create a parallel region where threads are spawned, and divide the work into tasks or work sharing constructs. For instance, in order to parallelize a SAXPY operation

$$\vec{y} := a\vec{x} + \vec{y} \tag{2.1}$$

the programmer could use one of the kernels in listing 2.1. These two approaches give the same results, although the internals of how the work is divided among the threads are different.

In the first code example the work in the for-loop is simply split between the threads. A default scheduling policy for work sharing is defined by the implementation, though a scheduling policy can be explicitly set.

In the second example, each iteration of the for-loop is defined as an independent *task*. Each task is then assigned to a thread by a task scheduler. The advantage of using tasks is that it is more dynamic; say that you have an implementation of merge sort that should be parallelized. Merge sort is a recursive sorting function, each call to merge sort calls the merge sort function on two halves of the input recursively. This is hard to accomplish using traditional work sharing, since the work is generated recursively. Using tasks, parallelization of such recursive routines is easily expressed by defining each call to merge sort as an independent task.

When writing OmpSs code for SMPs the code for the SAXPY routine is very similar to the task-based OpenMP code, but without the #pragma omp parallel block. The reason for this is that in OmpSs, the #pragma omp parallel block is implied threads are spawned when the application launches, so the parallel construct is redundant [25]. Listing 2.2 shows the code that runs with OmpSs. As with OpenMP, tasks are created with the #pragma omp task construct. These tasks are then scheduled to be exe-

#### Listing 2.1 Multi-threaded SAXPY in OpenMP

(a) SAXPY in OpenMP with work sharing

```

1

void saxpy_tasks(float* x, float* y, float a, int N) {

2

#pragma omp parallel

3

{

for (int i = 0; i < N; i++) {</pre>

4

#pragma omp task

5

6

{

7

y[i] = y[i] + a \times x[i];

}

8

9

}

10

}

}

11

```

(b) SAXPY in OpenMP with tasks

cuted on one of the threads. Note that work sharing can also be used in OmpSs like in OpenMP, but without the parallel directive.

Listing 2.2 Multi-threaded SAXPY in OmpSs

```

void saxpy_ompss(float* x, float* y, float a, int N) {

1

for (int i = 0; i < N; i++) {

2

#pragma omp task

3

4

{

y[i] = y[i] + a \star x[i];

5

}

6

7

}

8

//wait for all tasks to complete (synchronization point)

9

#pragma omp taskwait

10

}

```

#### 2.2.2 Heterogeneous capabilities

OmpSs can generate code for symmetric multiprocessors and thus function like traditional OpenMP, but it also supports creating tasks containing code for accelerators using CUDA and OpenCL, as well as Cell processors. The programmer still needs to write device-specific code, but details like data movement, device queries and setup is either hidden from the programmer, or simplified to simple directives.

Instead of having the programmer managing data movement on a device-specific level, OmpSs provides extensions to indicate what data needs to be moved into and out from the device(s) and any dependencies using the directives inout, input and output. For instance, listing 2.3 shows the program outline of SAXPY for both SMPs and OpenCL.

#### Listing 2.3 Heterogeneous OmpSs program

```

const int NB = 16;

2

#pragma omp task inout ([NB] y) input ([NB] x)

3

void saxpy_block (float* x, float* y, float a)

4

5

{

6

//SMP specific kernel code for computing y = y + ax for a block of size NB

7

}

8

#pragma omp target device (cell) copy_deps implements (saxpy_block)

9

void saxpy_block_cl (float* x, float* y, float a)

10

11

{

12

//OpenCL specific kernel code

13

}

14

void saxpy(float* x, float* y, float a, int N)

15

16

{

for (int i = 0; i < N; i + = NB)

17

18

{

//Generate the OmpSs tasks

19

20

saxpy_block(x+i, y+i, a);

21

22

#pragma omp taskwait

23

}

```

#### 2.2.3 Nanos++ and Mercurium

In the implementation of OmpSs used in this work, developed by BSC, the Nanos++ runtime system is used for task creation and scheduling. Mercurium is a source-tosource translator that takes the source code as input and translates all OmpSs #pragma omp directives into calls to the Nanos++ runtime.

#### **OmpSs in Mont Blanc** 2.2.4

OmpSs is targeted for use in the Mont Blanc project [1] and has been successfully used in a cluster environment [26]. A computer built on low power devices requires a higher number of computing cores than traditional CPUs in order to achieve the same performance, and the Mont Blanc prototypes will also be using accelerators like GPUs. Both of these points introduce complexities in the code that OmpSs attempts to address. It is as of yet uncertain if OmpSs will be used instead of, or in addition to MPI (Message Passing Interface) in Mont Blanc.

#### 2.2.5 Task scheduling and scheduling algorithms

In OmpSs, threads are spawned as soon as the application starts. The main thread runs serially through the program, and once a task is found, it adds this task to a shared task pool. The inactive worker threads then takes tasks from this pool, puts them into its own private pool of tasks and starts executing them [25]. The worker threads then selects tasks to execute based on the scheduling algorithm that is used.

Some scheduling algorithms utilize work stealing. These algorithms can steal tasks from other thread's private task pools. This can help in instances where the load

1

balance is uneven, but may suffer from less optimal memory locality.

The scheduling algorithm for OmpSs controls which tasks are executed by which thread, which order they are executed in and when they are executed. The choice of the scheduling algorithm can significantly affect the performance of applications in task-based programs [27], both because of memory locality issues, and because of how the tasks are generated. A breadth first algorithm generates all the tasks in the current recursion level before executing them, while a depth-first algorithm does a depth-first traversal of the tasks, and starts executing once the scheduler reaches the bottom-level task.

The default scheduling algorithm in the Nanos++ runtime was found to be depthfirst by inspection of the Nanos++ source code. In addition to the default algorithm, distributed breadth-first and work-first will be considered in this thesis. Distributed breadth-first is breadth-first with work stealing. Work-first is depth-first with work stealing.

In chapter 6 we see that choosing the right scheduler for the application has a significant impact on performance.

#### 2.3 Single Instruction, Multiple Data (SIMD)

In recent years, there has been considerable focus on parallelization of software due to the fact that the performance of single core CPUs at some point will reach a wall due to power, instruction level parallelism and memory bandwidth[28][29][30][31]. Increasing the operating frequency of a CPU usually comes with an increase in voltage, and because power is given by [32]

$$P = Cv^2 f \tag{2.2}$$

where C is the capacitance, v is the voltage and f is the frequency. We see that simply increasing the operating frequency, and thus also voltage, is not a sustainable strategy as it would at some point be impractically expensive to keep the chip cool enough.

If frequency stays constant, any increase in performance per processor core must come from an increase in work being done per clock cycle. This can be achieved by having each core execute more instructions per clock cycle, or letting each instruction process more data. The first point is achieved by pipelining the execution of instructions; however, due to data dependencies between instructions, this approach has limits. Introducing vector capabilities is another way of adding more computing power to a CPU core without increasing the frequency. In simplest terms, a CPU capable of vector operations can perform a single operation on multiple data elements at a time, thus is classified as Single Instruction, Multiple Data in Flynn's taxonomy, or SIMD for short.

Although CPUs have traditionally been used for general purpose computing, Graphics Processing Units (GPUs), which traditionally has been purely used for graphics, are now used in scientific applications due to their enormous computing power. GPUs typically get their computing power from vectorization; modern GPU architectures like NVIDIA Fermi uses vector lengths of up to 1024 bits (32 single-precision floating point values) [33], with tens of vector cores performing vector operations in parallel. These GPUs are typically slow on serial operations, so they are limited as a general purpose processor, and also due to the overhead of transferring data to and from the device memory. However, embedded low-power GPUs like the NVIDIA Tegra and ARM Mali GPUs operate with far fewer computing cores [34]. The ARM Mali can also directly access the host's main memory, so the datasets does not need to be explicitly transferred to the device. The NVIDIA Tegra and ARM Mali GPUs are both candidates for use in Mont Blanc [1].

Many modern processor architectures, for instance Intel Sandy Bridge and its predecessors, and the ARM Cortex series of CPUs are capable of doing vector operations on 128-bit vectors. x86 CPUs usually implement Streaming SIMD Extensions (SSE) instructions [35], while ARM CPUs often implement Advanced SIMD Extensions (NEON). In theory, these technologies can give up to four times speedup in execution from nonvectorized code for single precision, or two times speedup for double precision<sup>1</sup>. The newest x86 processors, like the Intel Sandy Bridge and Ivy Bridge, and AMD Bulldozer has support for Advanced Vector Extensions [3], which double the size of the vectors to 256 bits, giving a theoretical speedup of two compared to SSE, and up to eight compared to code not optimized for vector operations for single precision.

#### 2.3.1 Streaming SIMD extensions (SSE)

SSE, designed and introduced by Intel in 1999, is implemented in modern x86-based CPUs today. SSE is based on the older MMX instruction set with 64 bit registers introduced in 1996. The original SSE implementation had most of the basic floating point operations like addition, multiplication, data shuffling, bitwise operations and more for 128 bit registers. SSE2 brought 128-bit integer arithmetics, where SSE1 used the older 64-bit MMX registers for integer operations. SSE3 introduced the capability of working horizontally within a register in only a single instruction, e.g. horizontal reductions  $({A_0, A_1}, {B_0, B_1} \Rightarrow {A_0 + A_1, B_0 + B_1})$ , whereas vector operations traditionally are performed in a vertical fashion. SSE4 is the latest addition and adds instructions like dot products, min/max, blending, and more.

SSE SIMD instructions are similar to scalar instruction like fadd, fmul, etc., except they work with larger registers and multiple data elements at once. For instance, the vector instructions movps and addps corresponds to the scalar instructions for data movement and floating point addition mov and fadd. The vector instructions are performed on all four (or two, if double precision) elements in the vector in one operation.

In SSE there are 128 bit registers called xmm0 through xmm7; for 64-bit architectures (AMD64, Intel 64), there are eight additional registers xmm8 through xmm15. Typically, the programmer does not need to worry about registers as these are chosen by the compiler.

When creating programs in C that use SSE, there are three typical ways of vectorizing the code:

<sup>&</sup>lt;sup>1</sup>Note that NEON does not support double precision, so this only applies to SSE

- 1. Writing inline assembly. This is often hard to read, and gives the compiler little room for optimization, but gives the programmer complete control of the code.

- 2. Telling the compiler to create vector code automatically. This works well in some cases where it's easy to spot e.g. loops suitable for vectorization, but it is often hard for the compiler to spot code that can be vectorized.

- 3. Using intrinsics, which is basically wrappers around the assembly for the instructions. This gives the programmer close to total control while also giving the compiler the opportunity of optimizing, e.g. moving instructions around to maximize register use.

Listing 2.4 SAXPY in SSE

```

1

void saxpy_sse(float* x, float* y, float a, int N) {

__m128 _a = _mm_set1_ps(a);

for (int i = 0; i < N; i += 4) {</pre>

2

3

_m128 _x = _mm_loadu_ps(&x[i]),

4

_y = _mm_loadu_ps(&y[i]);

5

_y = _mm_add_ps(_y, _mm_mul_ps(_a, _x));

6

7

_mm_storeu_ps(&y[i]);

}

8

9

}

```

Listing 2.4 shows a simple program that performs SAXPY defined in Equation 2.1 using SSE intrinsics.

#### 2.3.2 Advanced Vector Extensions (AVX)

In 2008, Intel proposed the Advanced Vector Extensions (AVX), as a successor to SSE, with twice as large vector registers for theoretically twice the throughput for vector operations compared to that of SSE. As of writing this thesis, Intel's Sandy Bridge and Ivy Bridge-series, and AMD's Bulldozer processors support AVX. AVX instructions are very similar to SSE, except they work with larger vectors.

AVX registers are extensions of the SSE registers, reusing the 128 bit registers and adding another 128 bits on top of the xmm\* registers [36]. AVX registers are named the ymm registers.

#### Listing 2.5 SAXPY in AVX: y[i] := ax[i]+y[i]

```

void saxpy_avx(float* x, float* y, float a, int N) {

1

_m256 _a = _mm256_set1_ps(a);

2

3

for (int i = 0; i < N; i += 8)

_m256 _x = _mm256_loadu_ps(&x[i]),

4

5

_y = _mm256_loadu_ps(&y[i]);

_y = _mm256_add_ps(_y, _mm256_mul_ps(_a, _x));

_mm256_storeu_ps(&y[i]);

6

7

8

}

9

}

```

Programming with AVX is very similar to programming with SSE: Intrinsics, inline assembly or automatic vectorization can be used. Listing 2.5 shows a programming example with SAXPY, similar to that in section 2.3.1. As we see, the code is nearly identical, just with larger vectors and slightly different names for the intrinsics.

#### Transition between SSE and AVX

The SSE xmm registers is actually the lower half of the ymm registers used in AVX. Attempting to write to any of the xmm registers after writing to the ymm registers will make the CPU store the contents in the ymm registers to memory before allowing the xmm register to be written, and then writing it back again. This is costly and is called an AVX-SSE transition penalty [36].

Some compilers, e.g. gcc, generates SSE code automatically if it finds a candidate for optimization. This can trigger an AVX to SSE transition penalty, slowing down the execution of the SSE code significantly. To avoid AVX-SSE transition penalties, the instruction VZEROUPPER can be invoked to clear the upper halves of the ymm registers after use. This makes sure SSE code will not trigger the protection mechanism, as the CPU will know that the register is free. A corresponding intrinsic exists in gcc and icc, \_mm256\_zeroupper().

#### 2.3.3 ARM Advanced SIMD Extensions (NEON)

Advanced SIMD Extensions, also called NEON, is the SIMD architecture present in the ARM Cortex CPUs. NEON operates on 64-bit or 128-bit vectors containing elements of size 8, 16 or 32 bits. However, in contrast to SSE, NEON does not have 128-bit registers. Instead, two 64-bit registers are used to hold one 128 bit vector [37]. As a result, most vector arithmetics involving 128-bit vectors are performed separately for each of the 64-bit D registers holding the operands. This is also indicated by the timings for each instruction given at the ARM Infocenter website section for the Cortex-A9 architecture [38]. Consequently, the potential speedup for NEON is lower than that of SSE, because most single-precision floating point operations can only be performed on two floats per cycle.

```

Listing 2.6 SAXPY in NEON: y[i] := ax[i]+y[i]

```

```

1

2

3

4

5

6

7

8

```

9 }

Programming with NEON is similar to programming with AVX or SSE, although with different instructions. Intrinsics, inline assembly, and automatic vectorization are available in gcc. An example of SAXPY using NEON intrinsics in gcc is given in listing 2.6.

### 2.4 Energy Efficiency Metrics

This section discusses different metrics for energy efficiency. Energy, power, GFLOP-S/W, the energy-delay product and energy-delay squared product are discussed.

#### 2.4.1 Energy and power

Energy is measured in Joules, and power in Joule/second or Watts. Knowing the power dissipation for different optimization methods (e.g. SIMD, or multi-core) reveals information about the energy cost of the different methods.

#### 2.4.2 GFLOPS/W

It is interesting to note that using the terminology from section 1.3, the metric FLOPS/W is equivalent to flops/J, because FLOPS/W = (flops/s)/(J/s) = flops/J. Additionally, if the problem size, and then also # flops, is fixed, FLOPS/W is simply the reciprocal of the total energy spent scaled by a constant, i.e. the # floating point operations. This means that when GFLOPS/W is at a maximum, the energy spent is minimal, and vice versa.

The article "Models and Metrics to Enable Energy-Efficiency Optimizations" [39] discusses different metrics for energy efficiency. For instance, the authors propose the JouleSort benchmark, which measures the number of records that can be sorted per joule. This is similar to the metric flops/Joule, which is equivalent to FLOPS/W used in the Green500 lists as the measure of energy efficiency [11]; both measure the amount of work done per unit of energy, although the quantities are different (# elements sorted, and # flops).

#### 2.4.3 Energy-delay products

Power dissipation is given by equation 2.2, and since v is also dependent on f, reducing the frequency allows us to also reduce the core voltage, and thus the power. However, even though this would likely increase the FLOPS/W value, and reduce the total energy spent, the performance may be much lower. Horowitz et. al [40] proposed the energy-delay product to address this issue, which is defined as  $Energy \times Delay$ , often abbreviated as EDP. Because both power and performance is related to clock frequency and voltage, the idea is that the EDP would reveal the energy efficiency of the underlying processor design instead of having a metric directly dependent on the clock frequency [39].

#### **Energy-delay squared**

Martin et. al proposed a generalization of the energy-delay product on the form  $Energy \times Delay^n$  [41]. Here, *n* can be chosen emphasize performance in the energy-delay product. n = 2 is discussed thoroughly in the article as a reasonable choice for many applications. The article argues that the traditional EDP is not sufficient to compare implementations when voltage scaling is involved. It gives an example with a log and linear implementation of a comparator, where the energy usage of the log comparator is higher than the linear one if the voltages are the same, giving a higher EDP even if the delay is lower. However, when the voltage of the log comparator is scaled so that the delay matches that of the linear one, the energy spent is lower, and thus it is revealed that the log implementation is better. The  $ED^2$  metric reveals this even if the voltages are the same.  $ED^2$  is sometimes abbreviated to as EDD.

#### Technology scaling: Process-normalized EDP and EDD

If the transistor size due to the manufacturing process is scaled by a factor of  $\lambda$ , under ideal conditions, the energy-delay product is scaled by  $\lambda^4$  [40]. In the paper "Energy dissipation in general purpose microprocessors" [42], the authors argue that because the processor speed is limited by other factors like the memory system, and that there is a threshold voltage that cannot be subsided in order for the processor to function, the EDP scaling factor likely lies between  $\lambda^2$  and  $\lambda^3$ . The process-normalized EDP can then be given as

$$EDP_{normalized} = \frac{Energy \times Delay}{\lambda^s}$$

(2.3)

where *s* is the scaling factor and  $2 \le s \le 4$ . In [42],  $\lambda^2$  is used as the scaling factor in the processor comparisons, which is considered the lower-bound for the scaling factor [40].

Horowitz et. al. [40] state that the delay and energy is each reduced by a factor of  $\lambda$  due to reduced capacitance alone if the transistors are scaled with a factor  $\lambda$ . Although no papers defining a reasonable normalization factor for EDD was found, we will make an attempt to derive one. Since the EDD is simply EDP × *Delay* and if the normalization factor for the EDP is  $\lambda^s$ , we will use the normalization factor  $\lambda^{s+1}$ , as it simply counts the factor due to the delay twice. This gives the *normalized EDD*

$$EDD_{normalized} = \frac{Energy \times Delay^2}{\lambda^{s+1}}$$

(2.4)

#### 2.5 Related Work

In this section we present a selection of research papers, white papers and online resources related to the thesis.

#### 2.5.1 The Energy Efficiency of CMP vs SMT for Multimedia Workloads

Sasanka et. al compares the energy efficiency of chip multiprocessors (CMP) and singlecore processors utilizing simultaneous multi-threading (SMT) when applied to multimedia applications [43]. The authors models a dual-core and quad-core CMP, and two different SMT processors supporting two and four simultaneous threads, respectively. They use the normalized energy per instruction as the energy metric, and time per instruction for performance. CMPs are found to be more energy efficient; the dual-core use 9% less energy on average and the quad core use 39% less energy compared to SMTs with two and four threads, respectively.

A hybrid model with SMTs as cores in a CMP is also modelled, which is shown to use 11% more energy on average compared to the CMP. Intel multi-core processors with hyper-threading uses this hybrid model.

#### 2.5.2 Energy per Instruction Trends in Intel®Microprocessors

Grochowski et. al presents an overview of the trend of the energy consumption per instruction (EPI) in Intel processors from the 486 to the Intel Core Duo family [44]. The performance and energy is process-normalized in order to remove the factor of transistor size. The authors show a strong increase in the EPI up to the Pentium 4 Willamette processor with an EPI of 48nJ, and then almost an equally strong decrease down to an EPI of 11nJ for the Core Duo Yonah. As a comparison, the 486 processor is stated to have an EPI of 10nJ.

#### 2.5.3 Evaluation of OpenMP Task Scheduling Strategies

A part of this thesis is dedicated to finding a good scheduling algorithm for the benchmarked applications. A. Duran et.al shows that in many applications, the work-first algorithm works best [27]. The work-first algorithm attempts to follow the serial execution pattern of the application, and thus exploits memory locality that would be present as if the application were to be run serially. Breadth-first is another scheduling scheme where all tasks for the current recursion level is put in the task pool before execution of the tasks on the next recursion level commences. The authors finds that breadth-first algorithm is inferior to work-first in most of their benchmarks.

In this project, a different set of applications are benchmarked, and using OmpSs instead of OpenMP. The results in [27] are relevant and used as a guideline for what schedulers should be explored.

#### 2.5.4 Parallelization of Black-Scholes and dense matrix-matrix multiply using OmpSs

A. Duran et.al "OmpSs: A Proposal For Programming Heterogeneous Multi-Core Architectures" [25] presents results from performance benchmarks for both Black-Scholes and matrix-matrix multiply where OmpSs is used. The CPU-version of the matrixmatrix multiply algorithm performs at 4 GFLOPS with four cores for most problem sizes. For Black-Scholes, no absolute performance numbers are presented; instead, the paper presents speedups from increasing the number of threads. The speedups presented are against the serial version that does not use OmpSs. One thread using OmpSs tasks achieve 2.6x speedup due to the SIMD OpenCL kernel that is generated. For four threads, the speedup is 10, or 3.84 compared to the single threaded OmpSs implementation. The paper does not present energy efficiency results, which is the goal of this thesis.

#### 2.5.5 Benchmarking of FFTW

The FFTW library is extensively benchmarked in terms of performance on a variety of platforms [45][17][46]. The results show that FFTW has a definite peak around where the problem fits in the faster caches of the CPU, after which the performance drops. These papers presents impressive performance results for single-threaded execution versus other popular FFT algorithms, however no results was found on power consumption on different devices. Also, no benchmark was presented for newer processors using more than one core.

#### 2.5.6 Energy efficiency of IRAM architectures

Fromm et. al. presents energy efficiency models for IRAM architectures, where DRAM is integrated on the processor chip [47]. Because the DRAM is present on-chip, the authors argue that the energy consumption is reduced compared to using a traditional off-chip DRAM memory system. The authors found that the energy consumption of IRAM systems is significantly lower than systems using a conventional memory hierarchy. The paper uses the metric energy per instruction metric in the results.

#### 2.5.7 Green500

Green500 is a ranking website for energy-efficient supercomputers [11]. The site ranks the machines listed in the Top500 list by energy efficiency using GFLOPS/W, where the performance is measured using LINPACK, and the power is measured off the same benchmark. The Green500 Run Rules list specific guidelines and rules for how the measurements must be made [48]. As of November 2011, the top ranking computer is the IBM BlueGene/Q, Power BQC with 2.02 GFLOPS/W.

#### 2.5.8 Energy-saving mobile processor architectures

Goulding-Hotta et. al. presents an alternative to the traditional general purpose processor used in devices running the Android operating system [49]. The authors estimate a 91% reduction in energy consumption by using specialized circuits for commonly used functionality, like Fast Fourier Transforms or JPEG decompression. The reductions are possible because these chips do not need a instruction fetch/decode unit, instruction cache, register file or a generalized data path.

# Chapter 3

## **Application Kernels**

This chapter gives an overview of the application kernels that was chosen for benchmarking in this thesis.

Section 3.1 describes the Black-Scholes model and the application kernel, while section 3.2 gives a short description of fast Fourier transforms and their applications, as well as the FFTW library. Section 3.3 gives a brief overview of the matrix multiplication kernel.

#### 3.1 Black-Scholes (BSOP)

In this section the Black-Scholes model is explained. Black-Scholes were chosen because it has previously been benchmarked as an OmpSs application, and is part of the PAR-SEC Benchmark Suite for shared memory computers [50]. The Black-Scholes model is a mathematical model of a financial market, describing the price of an option over time [51]. An option in the financial sense of the word is a contract of selling and buying some underlying asset where one of the parties are obligated to sell/buy the asset, while the other party is not. This has financial value, as the party that is not obligated to do anything may choose whatever is most beneficial for him or her, even if that involves a financial loss for the other party. This price is what the Black-Scholes model attempts to model. The Black-Scholes equation is the partial differential equation given in equation 3.1.

$$\frac{\delta V}{\delta t} + \frac{1}{2}\sigma^2 S^2 \frac{\delta^2 V}{\delta S^2} + rS \frac{\delta^2 V}{\delta S} - rV = 0$$

(3.1)

where

S is the price of the underlying stock.  $\sigma$  is the volatility of the stock's returns.

V(S,t) is the price of a option.

t is the time, in years.

r is the annual risk-free interest rate.

From this differential equation, the Black-Scholes formula can be derived, which describes the price of European-style call and put options. A call option is an option

where the seller is required to sell if the buyer wants to buy, but the buyer is free to not buy the asset. A put option is the opposite, where the buyer is required to buy if the seller wants to sell the asset, but the seller may choose wether or not to sell. European style options are options that must be exercised at the time of maturity, i.e. the agreed point in time for the trade. As a contrast, American style options can be sold/bought at any point in time up until the time of maturity. The Black-Scholes formula is derived by setting the appropriate boundary conditions, and is shown in equations 3.2 through 3.5. The derivation of the formula is outside of the scope of this thesis but can be found in [51].

$$C(S,t) = N(d_1)S - N(d_2)Ke^{-r(T-t)}$$

(3.2)

$$P(S,t) = N(-d_2)Ke^{-r(T-t)} - N(-d_1)S$$

(3.3)

$$d_1 = \frac{\ln \frac{S}{K} + (r + \sigma^2/2)(T - t)}{\sigma\sqrt{T - t}}$$

(3.4)

$$d_2 = \frac{\ln \frac{S}{K} + (r - \sigma^2/2)(T - t)}{\sigma\sqrt{T - t}} = d_1 - \sigma\sqrt{T - t}$$

(3.5)

Here, the function N is the cummulative distribution function of the standard normal distribution, T - t is the time to maturity (the option matures at time T), and K is the strike price. The functions C and P is the call and put option prices, respectively. The rest of the symbols are explained after equation 3.1.

The formula can be trivially evaluated in parallel by computing the value of the options at each point of time *t* in parallel. The implementation of the Black-Scholes kernel is more thoroughly explained in chapter 4.

#### **3.2 Fastest Fourier Transform in the West (FFTW)**

This section describes the FFTW library that is used for benchmarking in this thesis. FFTW is a relevant library for many scientific applications, and is one of the libraries targeted for porting to Mont-Blanc. There has been considerable research in the area of discrete Fourier transforms, especially fast Fourier transforms (FFT). FFT is a very important class of algorithm, and its applications are seemingly endless: filtering (e.g. filtering noise, or doing high/low pass filtering) in both signal processing, image processing [52]; solving linear equations [53]; multiplication of large numbers [54], and more.

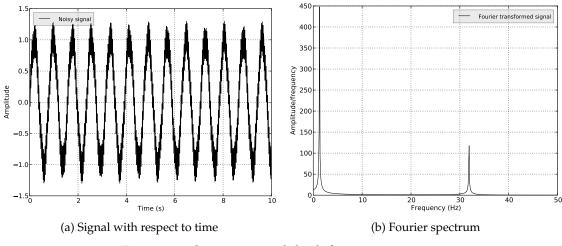

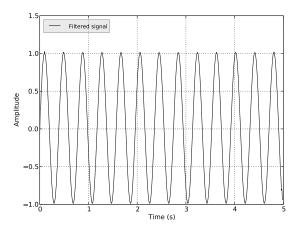

The discrete Fourier transform transforms a signal from the time or space domain to the frequency domain; this allows for a different view of the signal, for instance, instead of seeing periodic noise in an audio signal, we would see a peak in the frequency spectrum at the frequency of the signal. For instance, consider the signal in figure 3.1a. Here there is a signal with high-frequency noise added. If we apply a Fourier transformation on this signal and plot the amplitude of each frequency, we get the curve in figure 3.1b. We see that there are two peaks: One in the low frequency area (near zero on the x-axis, more specifically at about 1.27Hz), as well as one further out, at about 32Hz. That is the peak for the high-frequency noise.

Figure 3.1: Sine wave with high frequency noise

Setting the values of the high-frequency interval (roughly  $32Hz \pm 10Hz$ ) to zero for the transformed curve, and then performing an inverse transform yields the noise-reduced signal in figure 3.2.

Figure 3.2: Sine wave with noise filtered out

Computing the discrete Fourier transform naively takes  $O(n^2)$  time for *n* elements [55], which is too slow to be practical for many applications. However, the Fast Fourier Transforms is a class of algorithms designed to find the discrete Fourier transform in only  $O(n \log n)$  time [55]. It works by subdividing the problem into smaller pieces, e.g. splitting the input in half, and computing two smaller DFTs, which may be split further. We will not go deeper into the theory of FFTs as that is outside of the scope of this work.

The FFTW library is a library made for efficient computation of the Fourier transform and its inverse. It is regarded as one of the most efficient FFT libraries as it automatically tunes the algorithm to the machine it's run on, by first creating a plan of execution for the given problem, and then executing that plan. The plan is created by using some heuristics to adapt execution to the current system (e.g. querying the cache sizes), and also executing many different plans to find the best one. The plans may be saved to disk for reuse on other problems. Optionally, the measurement part may be left out to save time on creating the plan, yielding a less optimal plan for execution.

The FFTW plans contain information about how to most efficiently recursively subdivide the problem, and also how to most efficiently solve the base cases. The base cases are sufficiently small problems that can be solved directly using a series of small highly optimized code segments called *codelets*. When the plan is executed, the problem is subdivided according to the plan. Then, codelets are executed for each of the base cases.

### 3.3 Dense General Matrix-Matrix Multiplication and ATLAS

Matrix multiplication is a fundamental linear algebra operation which is used as a building block in many scientific applications. It is also a popular application for benchmarking due to its very high floating point operations-to-memory access ratio in the blocked implementation of this algorithm. Matrix-matrix multiplication is a level 3 BLAS (Basic Linear Algebra Subprograms) routine, and is generalized to

$$C = \alpha AB + \beta C$$

where A, B and C are matrices with dimensions  $m \times k$ ,  $k \times n$  and  $m \times n$ , respectively. The naive way of computing *AB* is simply calculating

$$C_{ij} = \sum_{l=1}^{k} A_{il} B_{lj} \tag{3.6}$$